In meinem Online Casino Test habe ich die meines Erachtens nach besten virtuellen Spielhallen miteinander verglichen. In meinem Testbericht führe ich die jeweiligen Unterschiede zwischen den verschiedenen Anbietern auf. Eines ist allen gemein: Sie arbeiten alle nicht mit einer deutschen Glücksspiellizenz, denn aufgrund der neuen Reglementierungen konnte mich kein Online Casino Deutschland mehr überzeugen. Dennoch verfügen alle von mir im Testbericht aufgeführten Spielangebote über eine gültige Lizenz.

Anbieter die im Online Casino Test am besten abgeschnitten haben

Wann gilt ein Online Casino als seriös?

Um ein Online Casino im Vergleichstest als seriös einstufen zu können, muss es einige wichtige Kriterien erfüllen. Die Seriosität gilt für mich als bestätigt, wenn

- eine gültige Glücksspiellizenz vorliegt

- ausschließlich renommierte Zahlungsdienstleister aufgeführt sind

- Auszahlungen zügig und zuverlässig bearbeitet werden

- nur geschulte, kompetente Support-Mitarbeiter eingesetzt werden

- die Spielersicherheit jederzeit gewährleistet ist

- Datenschutzbestimmungen eingehalten werden

- alle Spiele unter fairen Bedingungen angeboten werden

Das wurde getestet

In meinem Online Casino Test habe ich wichtige Testkriterien wie eine gültige Lizenz, das Casino-Spiele Angebot, die Seriosität und Sicherheit, sowie den Support und natürlich auch die Auszahlungsquoten in die Casino-Bewertung einfließen lassen. Meine Testsieger trumpfen mit Zuverlässigkeit, vorbildlichem Kundendienst und einer zügigen Gewinn-Auszahlung. Die Anbieter von virtuellen Spielautomaten, welche einen Platz in meiner Bestenliste gefunden haben, kann ich euch uneingeschränkt empfehlen.

In meinem Casinotest wie bei Stiftung Warentest habe ich alle wichtigen Kriterien berücksichtigt, allen voran die Seriosität der Anbieter, welche meiner Meinung nach immer gewährleistet sein muss. Mein Online Casino Betrugsstest ist auch keine Momentaufnahme, denn ich habe für den Online Casino Vergleich lange recherchiert, viel mit Echtgeld gespielt und mich monatelang mit den Vorzügen und Nachteilen der einzelnen Anbieter beschäftigt und auseinandergesetzt. Nur so kann ich einen unabhängigen Online Casino Test-Bericht liefern, für den ich nicht bezahlt werde und in den ich all meine Erfahrungen objektiv einfließen lassen kann. Von der Registrierung und Bonus-Inanspruchnahme bis hin zur Auszahlung meiner Gewinne wurden alle einzelnen Spielbereiche in sämtlichen Online Casinos durchlaufen und intensiv getestet.

Jeder einzelne Bereich wurde von mir kritisch unter die Lupe genommen und mit dem anderer Anbieter gegenüber gestellt und verglichen, um einen genauen Vergleich zu haben. Die Online Casinos in meinem Online-Casino-Test erhielten in mehreren, manche sogar in allen Rubriken eine sehr gute Casino Bewertung.

Nur seriöse Online Casinos schaffen es in meine Top 15 Casinos Bestenliste, denn so bleiben euch Enttäuschungen erspart, falls ihr euch für einen der von mir empfohlenen Anbieter entscheidet. Einen Online Casino Betrug müsst ihr also definitiv nicht befürchten, denn ich habe ausführlich mit Echtgeld gespielt und überall Auszahlungen beantragt. Keiner der oben aufgeführten Anbieter hat mir eine Auszahlung verweigert oder die Zahlung unnötig lange hinausgezögert.

Im genauen Konkurrenzvergleich spielt die Rangliste eher eine untergeordnete Rolle, denn was die Reihenfolge in meiner Casino-Bestenliste anbelangt, entscheiden dann vielleicht doch auch ein klein wenig meine persönlichen Vorlieben. Wie ich auf der Startseite in meiner Vorstellung bereits erwähnt habe, mag ich Tischspiele wie Roulette und Poker sehr. Deshalb könnte der Rang in meiner Casino-Beurteilung dementsprechend ein wenig mein Faible an Tablegames widerspiegeln. Was Video-Spiele und Slotautomaten angeht, dürften alle von mir getesteten Online Casinos mit ihrem Spielangebot ziemlich gleichauf sein. In meinem Online Casino Test wurden Slots nicht mitbewertet, weil sie in allen virtuellen Spielangeboten zu finden sind.

Internet-Spielhallen, die meine Mindestanforderungen an die bereits weiter oben erwähnten Kriterien nicht erfüllen, erscheinen erst gar nicht in meiner Online Casino Test Bestenliste.

Direkter Casino Vergleich im Online Casino Test

Silverplay Online Casino

- ✔️ Tischspiele

- ✔️ Jackpots

- ✔️ Live Casino

- ✔️ Sportwetten

- ✔️ Autoplay & Turbospin

- ✔️ kostenlose Demo-Spiele

- ✔️ Curaçao Lizenz

- ✔️ 1000 € Casino Bonus

- ✔️ Tools zur Selbstkontrolle

- ✔️ Krypto-Casino

- ❌ 1 EUR Limit

- ❌ 5-Sekunden Pause

- ❌ Video-Ident Verifizierung

- ❌ 1000 € mon. Limit

Quickwin Casino

- ✔️ Tischspiele

- ✔️ Jackpots

- ✔️ Live Casino

- ✔️ Sportwetten

- ✔️ Autoplay & Turbospin

- ✔️ kostenlose Demo-Spiele

- ✔️ Curaçao Lizenz

- ✔️ 500 € Casino Bonus + 200 Freispiele

- ✔️ Tools zur Selbstkontrolle

- ✔️ Krypto-Casino

- ❌ 1 EUR Limit

- ❌ 5-Sekunden Pause

- ❌ Video-Ident Verifizierung

- ❌ 1000 € mon. Limit

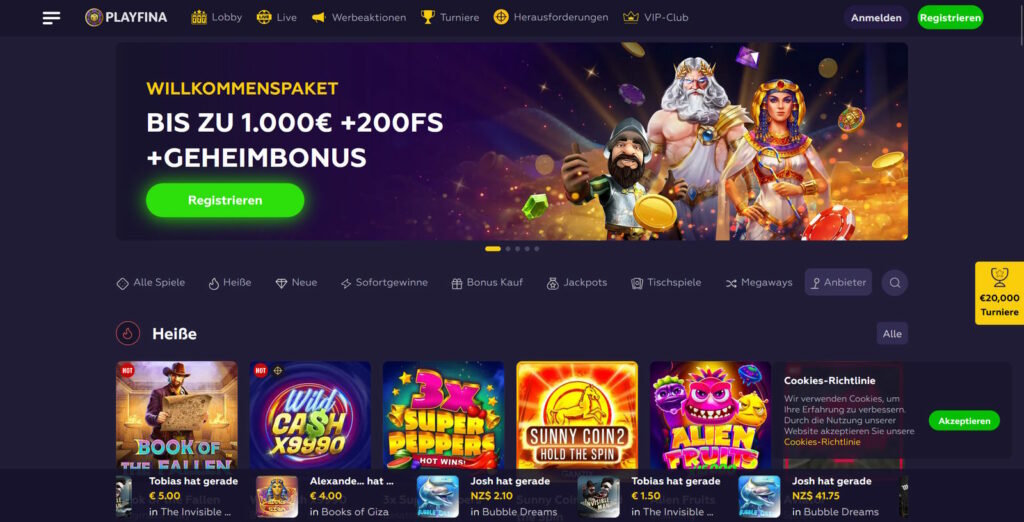

Playfina Casino

- ✔️ Tischspiele

- ✔️ Jackpots

- ✔️ Live Casino

- ❌ Sportwetten

- ✔️ Autoplay & Turbospin

- ✔️ kostenlose Demospiele

- ✔️ Curaçao Lizenz

- ✔️ 1000 € Casino Bonus + 200 Freispiele

- ✔️ Tools zur Selbstkontrolle

- ❌ Krypto-Casino

- ❌ 1 EUR Limit

- ❌ 5-Sekunden Pause

- ❌ Video-Ident Verifizierung

- ❌ 1000 € mon. Limit

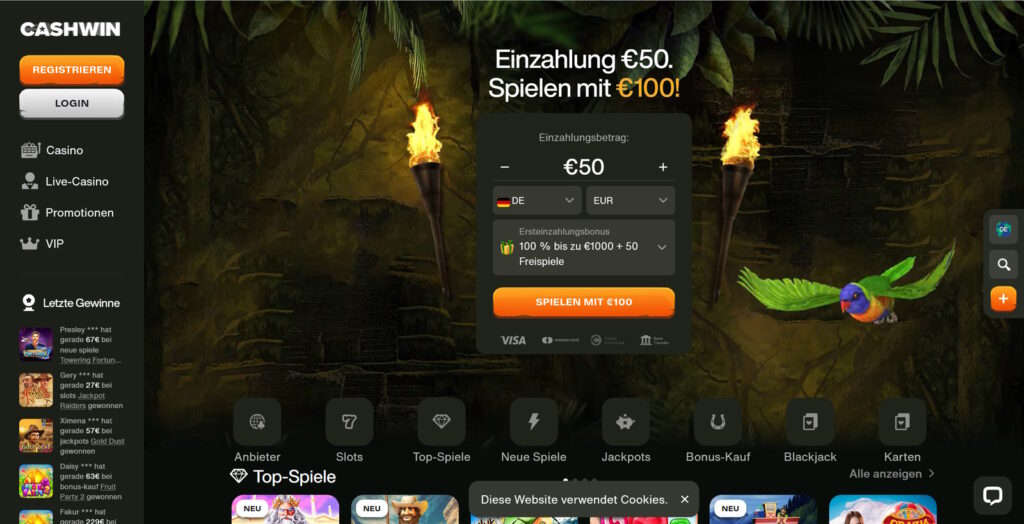

Cashwin Casino

- ✔️ Tischspiele

- ✔️ Jackpots

- ✔️ Live Casino

- ✔️ Sportwetten

- ✔️ Autoplay & Turbospin

- ✔️ kostenlose Demo-Spiele

- ✔️ Antillephone N.V. Lizenz

- ✔️ 1000 € Casino Bonus + 50 Freispiele

- ❌ Tools zur Selbstkontrolle

- ✔️ Krypto-Casino

- ❌ 1 EUR Limit

- ❌ 5-Sekunden Pause

- ❌ Video-Ident Verifizierung

- ❌ 1000 € mon. Limit

RollingSlots Casino

- ✔️ Tischspiele

- ✔️ Jackpots

- ✔️ Live Casino

- ❌ Sportwetten

- ✔️ Autoplay & Turbospin

- ✔️ kostenlose Demo-Spiele

- ✔️ Curaçao Lizenz

- ✔️ 500 € Casino Bonus + 100 Freispiele

- ❌ Tools zur Selbstkontrolle

- ✔️ Krypto-Casino

- ❌ 1 EUR Limit

- ❌ 5-Sekunden Pause

- ❌ Video-Ident Verifizierung

- ❌ 1000 € mon. Limit

Magical Spin Casino

- ✔️ Tischspiele

- ✔️ Jackpots

- ✔️ Live Casino

- ❌ Sportwetten

- ✔️ Autoplay & Turbospin

- ✔️ kostenlose Demo-Spiele

- ✔️ Antillephone N.V. Lizenz

- ✔️ 3000 € Casino Bonus + 50 Freispiele

- ✔️ Tools zur Selbstkontrolle

- ❌ Krypto-Casino

- ❌ 1 EUR Limit

- ❌ 5-Sekunden Pause

- ❌ Video-Ident Verifizierung

- ❌ 1000 € mon. Limit

Zet Casino Online

- ✔️ Tischspiele

- ✔️ Jackpots

- ✔️ Live Casino

- ✔️ Sportwetten

- ✔️ Autoplay & Turbospin

- ✔️ kostenlose Demo-Spiele

- ✔️ Antillephone N.V. Lizenz

- ✔️ 500 € Casino Bonus + 200 Freispiele

- ❌ Tools zur Selbstkontrolle

- ❌ Krypto-Casino

- ❌ 1 EUR Limit

- ❌ 5-Sekunden Pause

- ❌ Video-Ident Verifizierung

- ❌ 1000 € mon. Limit

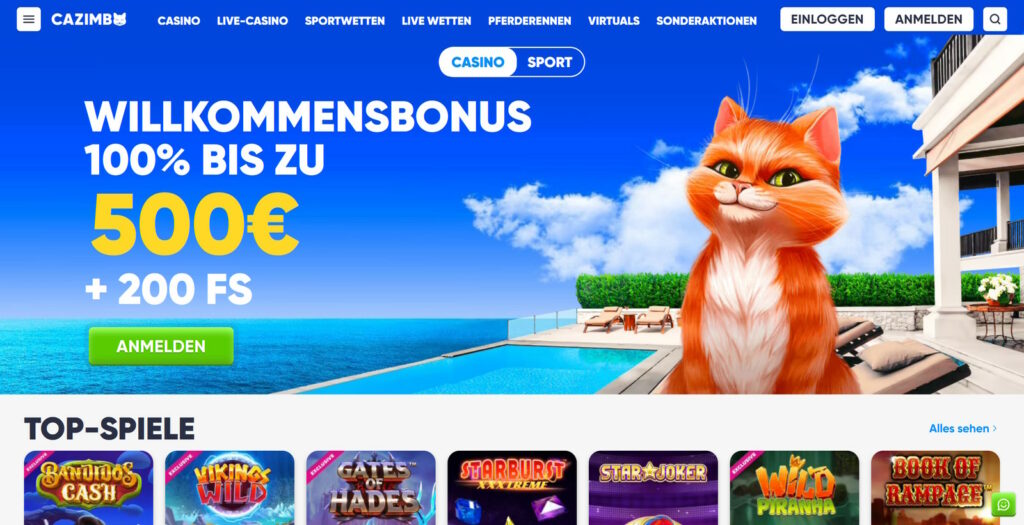

Cazimbo Casino

- ✔️ Tischspiele

- ✔️ Jackpots

- ✔️ Live Casino

- ✔️ Sportwetten

- ✔️ Autoplay & Turbospin

- ✔️ kostenlose Demo-Spiele

- ✔️ Curaçao Lizenz

- ✔️ 500 € Casino Bonus + 200 Freispiele

- ✔️ Tools zur Selbstkontrolle

- ✔️ Krypto-Casino

- ❌ 1 EUR Limit

- ❌ 5-Sekunden Pause

- ❌ Video-Ident Verifizierung

- ❌ 1000 € mon. Limit

Boomerang Casino

- ✔️ Tischspiele

- ✔️ Jackpots

- ✔️ Live Casino

- ✔️ Sportwetten

- ✔️ Autoplay & Turbospin

- ✔️ kostenlose Demo-Spiele

- ✔️ Curaçao Lizenz

- ✔️ 500 € Casino Bonus + 200 Freispiele

- ✔️ Tools zur Selbstkontrolle

- ✔️ Krypto-Casino

- ❌ 1 EUR Limit

- ❌ 5-Sekunden Pause

- ❌ Video-Ident Verifizierung

- ❌ 1000 € mon. Limit

AmunRa Casino

- ✔️ Tischspiele

- ✔️ Jackpots

- ✔️ Live Casino

- ✔️ Sportwetten

- ✔️ Autoplay & Turbospin

- ✔️ kostenlose Demo-Spiele

- ✔️ Curaçao Lizenz

- ✔️ 500 € Casino Bonus + 200 Freispiele

- ✔️ Tools zur Selbstkontrolle

- ✔️ Krypto-Casino

- ❌ 1 EUR Limit

- ❌ 5-Sekunden Pause

- ❌ Video-Ident Verifizierung

- ❌ 1000 € mon. Limit

Shiny Wilds Casino

- ✔️ Tischspiele

- ✔️ Jackpots

- ✔️ Live Casino

- ❌ Sportwetten

- ✔️ Autoplay & Turbospin

- ✔️ kostenlose Demo-Spiele

- ✔️ Curaçao Lizenz

- ✔️ 2000 € Casino Bonus + 150 Freispiele

- ✔️ Tools zur Selbstkontrolle

- ✔️ Krypto-Casino

- ❌ 1 EUR Limit

- ❌ 5-Sekunden Pause

- ❌ Video-Ident Verifizierung

- ❌ 1000 € mon. Limit

Casino Infinity

- ✔️ Tischspiele

- ✔️ Jackpots

- ✔️ Live Casino

- ✔️ Sportwetten

- ✔️ Autoplay & Turbospin

- ✔️ kostenlose Demo-Spiele

- ✔️ Antillephone N.V. Lizenz

- ✔️ 500 € Casino Bonus + 200 Freispiele

- ✔️ Tools zur Selbstkontrolle

- ✔️ Krypto-Casino

- ❌ 1 EUR Limit

- ❌ 5-Sekunden Pause

- ❌ Video-Ident Verifizierung

- ❌ 1000 € mon. Limit

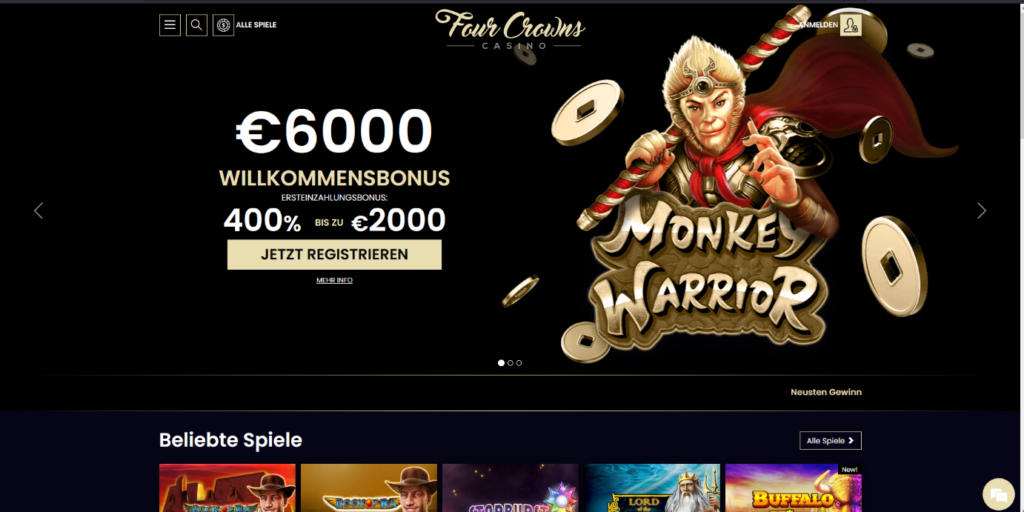

Four Crowns Casino

- ✔️ Tischspiele

- ✔️ Jackpots

- ✔️ Live Casino

- ❌ Sportwetten

- ✔️ Autoplay & Turbospin

- ❌ kostenlose Demo-Spiele

- ✔️ Curacao EGaming Lizenz

- ✔️ 6000 € Casino Bonus ohne Freispiele

- ❌ Tools zur Selbstkontrolle

- ✔️ Krypto-Casino

- ❌ 1 EUR Limit

- ❌ 5-Sekunden Pause

- ❌ Video-Ident Verifizierung

- ❌ 1000 € mon. Limit

Casombie Casino

- ✔️ Tischspiele

- ✔️ Jackpots

- ✔️ Live Casino

- ❌ Sportwetten

- ✔️ Autoplay & Turbospin

- ✔️ kostenlose Demo-Spiele

- ✔️ Antillephone N.V. Lizenz

- ✔️ 7 verschiedene Boni verfügbar

- ✔️ Tools zur Selbstkontrolle

- ✔️ Krypto-Casino

- ❌ 1 EUR Limit

- ❌ 5-Sekunden Pause

- ❌ Video-Ident Verifizierung

- ❌ 1000 € mon. Limit

Winny Casino

- ✔️ Tischspiele

- ✔️ Jackpots

- ✔️ Live Casino

- ❌ Sportwetten

- ✔️ Autoplay & Turbospin

- ✔️ kostenlose Demo-Spiele

- ✔️ Malta Gaming Authority Lizenz

- ✔️ 250 € Casino Bonus ohne Freispiele

- ✔️ Tools zur Selbstkontrolle

- ❌ Krypto-Casino

- ❌ 1 EUR Limit

- ❌ 5-Sekunden Pause

- ❌ Video-Ident Verifizierung

- ❌ 1000 € mon. Limit

Wie ihr unschwer erkennen könnt, bieten sämtliche in meinem objektiven Online Casino Test aufgeführten virtuellen Spielotheken Tischspiele, Jackpots, Live Casino Spiele und natürlich jede Menge Slotautomaten an, die ich in der Online Casino-Bewertung nicht gesondert aufgeführt habe. Video-Slots und Automatenspiele in einem Online-Casino gehören schließlich einfach dazu. Zusätzlich könnt ihr bei einzelnen Anbietern auch Sportwetten platzieren. Im direkten Online Casino Vergleich sieht man, dass die bewerteten Casinos sich nicht großartig voneinander unterscheiden.

Die in der Online Casino Test aufgeführten Betreiber verfügen alle über eine gültige Glücksspiellizenz aus Malta oder den Niederländischen Antillen (Curacao). Deutsche Online Casinos mit DE-Lizenz sind nicht aufgeführt, denn sie konnten mich bei der Casino Beurteilung aufgrund der vielen Einschränkungen gemäß der Glücksspielregulierung Deutschlands aus 2021 in kaum einem Kritikpunkt wirklich überzeugen.

Im Online Casino Testbericht sind ausschließlich Anbieter zu finden, welche ihre Spielhalle ohne 1€ Limit, ohne 5 Sekunden Regel und ohne monatliches Einzahlungslimit von 1000 € betreiben. Weiterhin sind bei Slotautomaten die Turbo-Spin und die Auto-Spin Funktionen verfügbar.

Wie ist der Ablauf beim Online Casino Test?

Zunächst widme ich mich der Recherche und schaue, welche neueren (oder auch älteren) Online Casinos es aktuell in der Branche gibt. Dank meiner jahrelangen Erfahrung im Glücksspiel-Sektor sehe ich häufig bereits auf den ersten Blick, ob es sich lohnt ein Spielangebot genauer unter die Lupe zu nehmen. Ich mag klar aufgegliederte Online Casinos, die es auch Neueinsteigern ermöglichen, sich schnell zurecht zu finden.

Wie ist der Ersteindruck?

Zunächst schaue ich mir die einzelnen Casinobereiche des Spielangebots ohne Registrierung an. Ist die Navigation übersichtlich? Gibt es eine Suchfunktion? Welche Software-Entwickler stellen ihre Spiele zur Verfügung? Gibt es alle Spielarten oder werden beispielsweise keine Tischspiele angeboten? Sind einzelne Spielbereiche klar aufgegliedert oder muss man umständlich suchen?

Lizenz und AGBs prüfen

Da der Ersteindruck manchmal auch täuscht, gehe ich danach relativ gezielt vor. Ein Scroll an das Seitenende gehört mit zu den ersten Dingen, die ich beim Besuch eines mir unbekannten Casinos mache. Liegt eine gültige Lizenz vor? Welches Unternehmen steht hinter der virtuellen Spielhalle? Sind die Allgemeinen Geschäftsbedingungen und Datenschutzrichtlinien in meiner Sprache oder zumindest in Englisch hinterlegt? Dies sind die ersten Schritte, die jeder verinnerlichen und in neuen Casinos machen sollte, denn hier trennt sich meist schon die Spreu vom Weizen. Generell gilt: Finger weg von Online Casinos ohne gültige Lizenz!

Registrieren und Bonus begutachten

Für einen aussagekräftigen Online Casino Test ist eine Registrierung unumgänglich. Als nächstes erstelle ich mir also ein Spielerkonto. An dieser Stelle wird in den meisten Fällen auch der Willkommensbonus angeboten, welcher von mir immer genau unter die Lupe genommen wird. Manche Anbieter versteckt Klauseln in den Bonusumsatzbedingungen, die ein Durchspielen in einem viel zu kurzen Zeitraum meist unmöglich machen. Casino-Newbies fallen allzu oft Bonus-Lockangeboten zum Opfer, denn sie sind nicht mit den Bedingungen vertraut, die man mit aktivem Bonusguthaben beachten muss.

Bonusumsatzbedingungen prüfen

Bei meinem Online Casino Test spielen auch die Bonusbedingungen eine Rolle. Wie hoch ist der Mindesteinzahlungsbetrag für den Bonus? Wie viel Bonusguthaben kann man im Höchstfall erhalten und wie hoch muss die Echtgeld-Einlage dafür sein? Welche Umsatzbedingungen gelten? Müssen sowohl die Einzahlung als auch das Bonusguthaben umgesetzt werden oder lediglich der Bonusbetrag? Welche Spiele sind vom Bonusspiel ausgeschlossen und zu welchem Prozentsatz zählen verschiedene Spielarten in die Setzbedingungen? Gibt es kostenlose Freispiele und welche Umsatzbedingungen gelten für die Gratisrunden? Wie lange habe ich Zeit, die Setzbedingungen zu erfüllen? Nur wenn die Antworten auf all diese Fragen zu meiner Zufriedenheit ausfallen, entscheide ich mich für das Bonusspiel. Ansonsten verzichte ich auf das Gratisguthaben im Casino.

Einzahlung tätigen

Wer einen Online Casino Test durchführen will, kommt natürlich nicht umhin, ein wenig Echtgeld zu opfern. Ich selbst bevorzuge mittlerweile Bitcoin Casinos, was aber nicht in die Bewertung in meinem Online Casino Test eingeflossen ist. Schließlich besitzt nicht jeder Kryptowährung. Alle virtuellen Spielcasinos aus meinem Online Casino Test akzeptieren den Euro als Zahlungsmittel und auch andere Währungen. Wichtig ist, dass für Einzahlungen mehrere unterschiedliche, vertrauenswürdige Zahlungsmethoden zur Auswahl stehen und alle Transaktionen verschlüsselt stattfinden. Diese Kriterien konnten auch alle Anbieter erfüllen, die ich in meinem Online Casino Test und in der Top 15 Casinos Auflistung berücksichtigt habe.

Spiele ausprobieren und Gewinne erzielen

Der schönste aber nicht wichtigste Teil in einem Online Casino Test ist das Spielen. Welche Spielarten bieten die unterschiedlichen Spielhallen an? Wie viele und vor allem welche Spiele-Provider sind verfügbar? Werden viele Genres berücksichtigt und wie umfangreich ist das Spielangebot? Fast alle Anbieter in meinem Online Casino Test halten Demo-Spiele bereit, die man nach Wunsch kostenlos spielen kann. Sehr beliebt sind die Entwickler Microgaming, Play'nGo, NetEnt und Merkur. Die meisten Betreiber haben die namhaftesten Spielemacher mit ins Boot genommen und halten somit die besten Spielautomaten bereit. Je mehr Anbieter, desto umfangreicher und abwechslungsreicher sind die Spielmöglichkeiten.

Verifizierung für Gewinnauszahlung

Sobald man sich seine Gewinne auszahlen lassen möchte, ist eine Verifizierung fällig. Im Online Casino Deutschland muss man sich mittlerweile direkt bei der Registrierung mittels Video-Ident Verfahren verifizieren, was ziemlich nervig sein kann und für manchen keine Option ist. Die Anbieter aus meinem Online Casino Test verzichten durchweg auf die Video-Identifizierung und fordern stattdessen nur die Kopie eines gültigen Ausweisdokuments. Hierfür reicht es aus, wenn man den Personalausweis beidseitig einscannt oder den Reisepass, und das Dokument per Mail an den Support sendet. Einige Anbieter halten auch ein Online-Formular dafür bereit, in das man die Datei hochladen kann.

Gewinne auszahlen lassen

Auszahlungen aus seinem Spielerkonto kann man gewöhnlich im internen Kundenbereich beantragen. Hier gibt man den gewünschten Auszahlungsbetrag an und wählt den passenden Zahlungsdienstleister aus. Ist die Verifizierung bereits erfolgt, wird die Auszahlung bei den Anbietern aus meinem Online Casino Test direkt bearbeitet, zumindest innerhalb 24 Stunden, und in die Zahlung in die Wege geleitet. Wallet-Zahlungen über Skrill oder Neteller gehen ruck zuck, Banküberweisungen können ein paar Tage beanspruchen, was aber am Zahlungsinstitut liegt und nicht am Online Casino. Meine Auszahlungen waren bei sämtlichen virtuellen Spielhallen aus meinem Online Casino Test schnell und reibungslos abgewickelt.

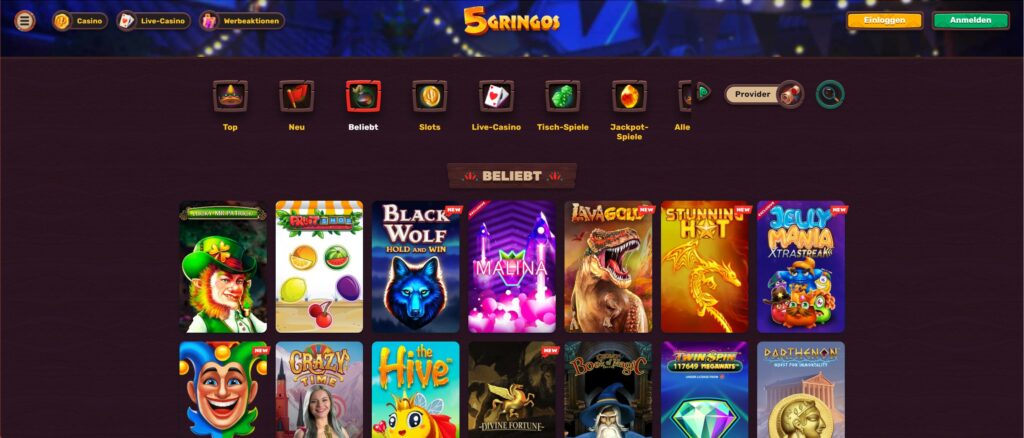

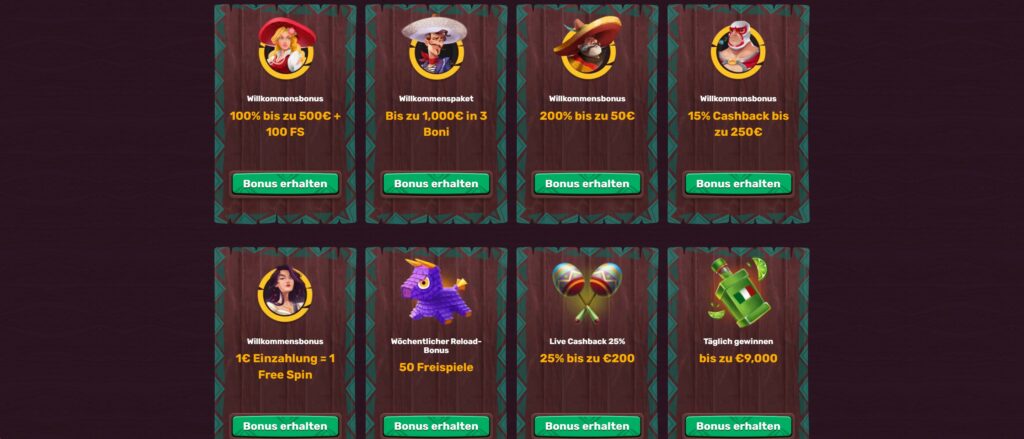

Testsieger im Online Casino Test – 5Gringos Online Casino

Mein absoluter Favorit im Online Casino Test, der in den meisten Kriterien-Punkten überzeugen konnte, ist das 5Gringos Online Casino (hier den Testbericht lesen). Es enthält alle Spielarten in den verschiedensten Genres und bringt mit knapp 3000 Casinospielen von mehr als 50 Software-Entwicklern reichlich Abwechslung in den Spieleralltag. Lizenzgeber ist die Antillephone N.V. aus Curacao und hinter dem Angebot steht das Unternehmen Rabidi N.V., mit Geschäftssitz in Willemstad/Curacao.

Der Willkommensbonus von bis zu 500 € und 100 Free Spins ist auf die ersten drei Einzahlungen aufgeteilt und ab einem Einzahlungsbetrag von nur 20 € verfügbar. Es stehen zahlreiche vertrauenswürdige Zahlungsinstitute für verschlüsselte Geld-Transaktionen zur Verfügung.

5Gringos setzt auf 100%ige Kundenzufriedenheit, was sich auch am rund um die Uhr verfügbaren Support bemerkbar macht. Kundenanfragen können zudem in mehreren Sprachen beantwortet werden und die geschulten Mitarbeiter sind in allen Bereichen kompetent.

Bei meinem Online Casino Test wurden alle Kontroll-Fragen innerhalb kürzester Zeit mehr als zufriedenstellend beantwortet. Den Bonus konnte ich problemlos durchspielen und meine Gewinnauszahlung verlief innerhalb einer Stunde ohne besondere Vorkommnisse zügig ab. Hierbei habe ich allerdings ein Skrill-Wallet genutzt. Je nach Zahlungsmethode kann es auch bis zu einer Woche dauern, bis die Beträge auf eurem Konto erscheinen.

Fazit zum Online Casino Test

Ich persönlich habe meinen Favoriten gefunden, spiele aber auch häufig noch bei den anderen Anbietern, die es in meinem Online Casino Test in die Top 15 Casinos Übersicht geschafft haben. Alle fünfzehn Online Spielhallen sind empfehlenswert und es entscheidet letzten Endes euer Geschmack, welches ihr als Favoriten empfindet. Jedes der Casinos ist durch eine Lizenz ausgezeichnet und wird staatlich reguliert, auch wenn die Regulierung nicht so streng ausfällt, wie es in Online Casinos mit deutscher Lizenz der Fall ist.

Fakt ist, dass auch bei einer EU-Lizenz ein Auge auf die finanzielle Lage des Anbieters geworfen wird und der Betreiber ein Lizenzierungsverfahren durchlaufen muss, um als 100% seriös eingestuft zu werden. Anders gibt es keine Lizenz. Beim Online Casino Deutschland liegt das Augenmerk bei der strengen Regulierung eher auf der Suchtprävention. Über Sinn oder Unsinn lässt sich bekanntlich streiten. Jedenfalls bevorzuge ich Online Casinos, die mich nicht so sehr im Spielen und meiner persönlichen Freiheit einschränken.

Häufige Fragen zu Online Casino Tests

Wie laufen Casinotests ab?

Zunächst wird nach aktuellen Online Casinos gesucht, die für einen Casino-Test in Frage kommen. Der erste Eindruck muss schon passen, damit ich mir überhaupt die Mühe mache, das Spielangebot näher in Augenschein zu nehmen. Danach überprüfe ich zunächst die Lizenz und ob alle Sicherheitsmaßnahmen stimmig sind. Hierzu gehören die AGBs und die Datenschutzbestimmungen. Erst danach wird das Spielangebot und der Support getestet. Nur wenn ich in ganzer Linie überzeugt wurde, schafft es ein Anbieter in meinem Online Casino Test einen Platz in der Casino Bestenliste zu erhalten.

Welche Casinos sind im Online Casino Test die besten?

Die besten Online Casinos im Test überzeugen auf ganzer Ebene. Sowohl die Sicherheit der Spieler wird dabei berücksichtigt, als auch die Spielauswahl, Auszahlungsquoten und die Qualifikation der Kundendienstmitarbeiter. Da mich deutsche Anbieter aufgrund der vielen Einschränkungen nicht mehr zum Spielen bewegen können, konzentriere ich mich eher auf Online Casinos mit EU-Lizenz aus Malta, Curacao, Gibraltar oder anderen europäischen Ländern.

Sind Casino Testberichte seriös?

Hier muss man ein wenig aufpassen. Manche Testberichte werden gesponsert und dementsprechend werden die Platzierungen der verschiedenen Anbieter in den Top 10 Casino-Listen ausfallen. Wer am meisten zahlt, landet oben. Ich habe die Online Casinos aus meiner Bestenliste alle selbst getestet und ein objektives Urteil gefällt. Deshalb landen bei mir nur Anbieter in der Top 10, die ihre Platzierung auch tatsächlich verdient haben.

Letztes Update am 24. März 2025 von Clifford Wolf's

- Die besten online Casinos ohne Echtgeld im Jahr 2026 - 26. Juni 2025

- Online Casinos mit schneller Auszahlung - 6. Mai 2025

- Online Casinos ab 1 Euro Einzahlung - 28. Mai 2024